Download Original PDF

Get the official Barkatullah University print version scanned document.

🤝 Help Your Juniors!

Have previous year question papers that aren't on our website? Help the next batch of students by sending them to us! With your consent, we will proudly feature your name as a Top Contributor on our platform.

Submit Papers 📩Roll No.

(d) Define Synchronous and asynchronous counter.

(e) Differentiate between PAL & PLA Devices.

Total No. of Questions : 6

[Total No. of Printed Pages : 4

EY-160

B.Tech. IIIrd Semester (New Scheme)

Examination, 2023-24

Digital System Design

Paper - EL - 304

Time : 3 Hours]

[Maximum Marks : 60

Note :-Ques. no. 1 is compulsory. Attempt any two parts from remaining questions.

1.

Write short answers.

(a) What are don't care conditions ?

(b) What is the difference between Encoder and multiplexer.

(c) What is toggle state in JK Flip-Flop.

(d) Define Synchronous and asynchronous counter.

(e) Differentiate between PAL & PLA Devices.

2.

(a) Solve the following Boolean function using KMAP in SOP form.

(i) F = k'lm + k'm'n' + klm'n + lmn'

(ii) F = Σ (5,6,7,8,9,12,13,14,15)

(b) Solve the following Boolean function using KMAP in POS form:

(i) F = x'z + w'xy' + w (x'y + xy')

(ii) F = A'B'D' + A'C'D + A'B'C:

d = A'B'C'D + ACD + AB'D' (d : don't care)

(c) Solve the following Boolean function using Tabulation method

F (a, b, c. d) = Σ (0,5,7,8,9,10,11,14,15)

3.

(a) A combinational circuit is defined by the following three equation :

F1 = x'y' + xyz'

F2 = x' + Y

F3 = xy + x'y'

Design the circuit with decoder and external gates.

(b) Implement the following Boolean function using 8 × 1 Multiplexer

Y (A,B,C,D,) = Σ (1,2,5,6,7,8,10,12,13,15)

(c) Design a combination circuit that converts 4bit binary code to gray code.

4.

(a) Draw the logic diagram of clocked SR Flipflop, include Preset and clear inputs. Give it's truth table. characteris-tic table and excitation table.

(b) Draw and explain the logic diagram Bi directional shift register with parallel load.

(c) Explain the working JK master Slave flip- Flop with suit-able diagram.

5.

(a) Design a mod-12 binary synchronous counter using JK FF. draw state table and state diagram.

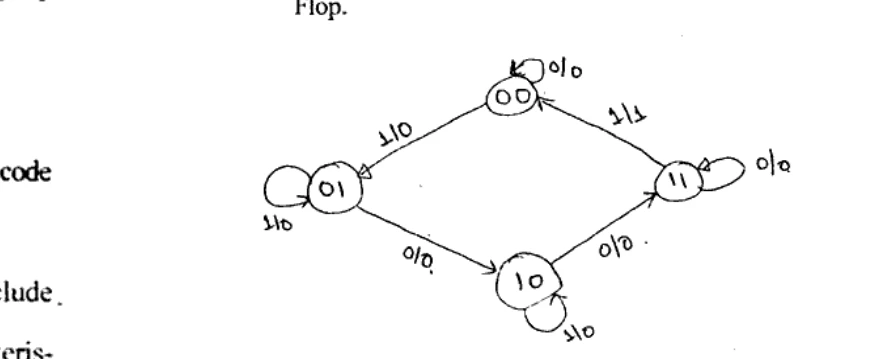

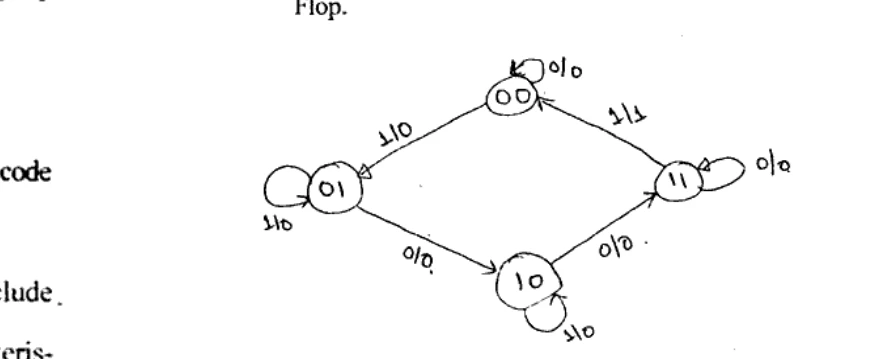

(b) For the following state diagram of a synchronous counter, draw state table and design the counter using T Flip-Flop.

(c) Design a synchronous counter with the following binary sequence 0,2,5,6,7 and repeat. Use SR Flip-Flop.

6.

(a) Design a sequence detector circuit for the sequence 1011100.

(b) Design and implement a full subtractor circuit using ROM.

(c) Write short note on CPLD.